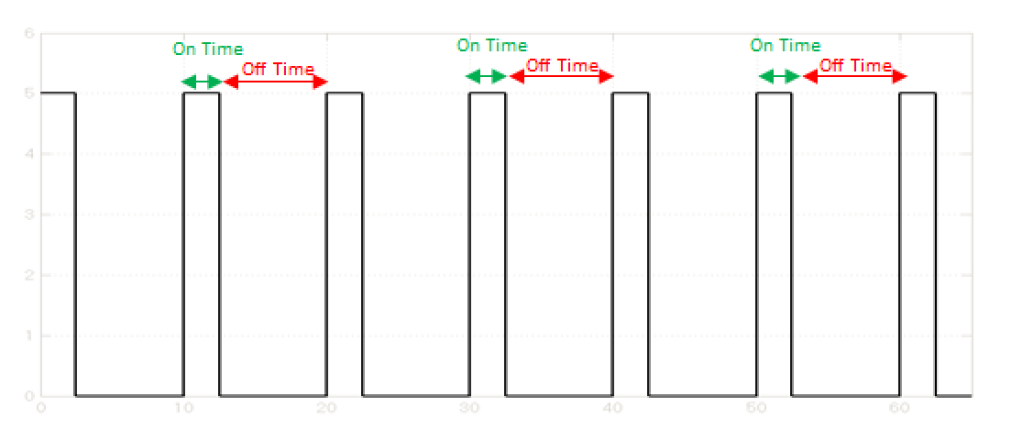

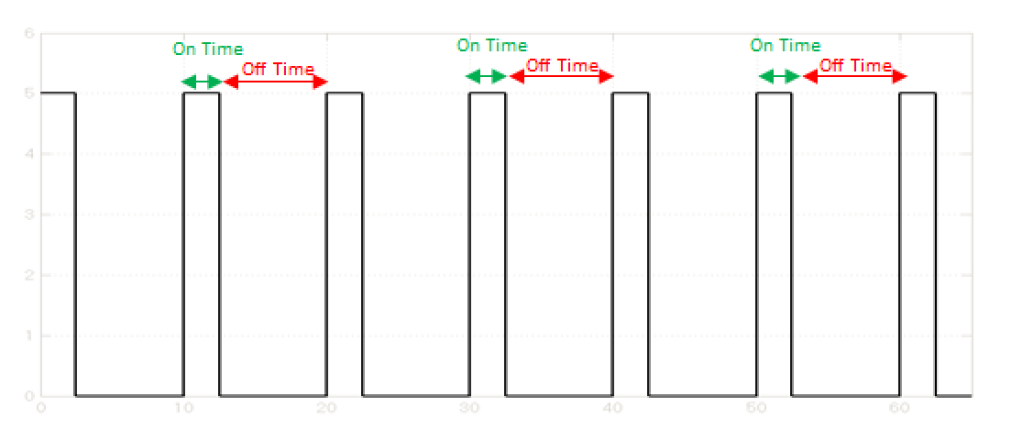

Figure 1: Typical PWM Signal

The CP-PWM-1112 is an FPGA-based Pulse Width Modulation (PWM) input card by Concurrent Real-Time. This card is designed to capture pulse-width-modulated signals with high accuracy. With a timing resolution of 15.15 ns, and the ability to measure the frequency and duty cycle of a signal, this card is ideal for use in hardware-in-the-loop (HIL) applications.

This PCIe card has 12 TTL input channels, with a frequency range of 0.05 Hz to 660KHz. Each channel has programmable digital debouncing filters and pulse-width averaging. The base measurement frequency of the card is 66 MHz with a pulse-width accuracy of 30.30 ns. You can use multiple cards on a system.

Figure 1: Typical PWM Signal

CP-PWM-1112.

WCS-PWM-1112.

ICS-SWB-1243.

Channel SettingsThe following settings apply to all channels:

I/O Device MappingAs with any other SimWB I/O devices, connection between the RTDB and the PWM Input card is done via the GUI mapping dialog. For each of the 12 channels, you can map the following measurements to AI RTDB variables:

Pin Assignment

|

|