|

|

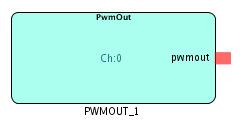

The PWM_OUTPUT block provides the ability to output a Pulse Width Modulation (PWM) pulse pattern based on the PWM frequency and dutycycle input. This IP Core provides functionalities such as:

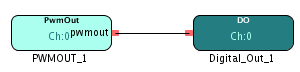

The digital output from the PWM_OUTPUT block is connected to the input of the digital output block.

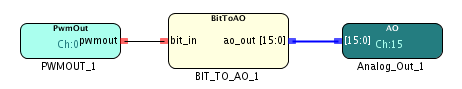

Digital output from the PWM_OUTPUT block is scaled and converted to a two level multi-bit value using the BIT_TO_AO block and then passed on to the analog output pin 15. A 0 coming from the PWM_OUTPUT block is converted to -5V on the analog channel and a 1 coming from the PWM_OUTPUT block is converted to a +5V signal.