|

|

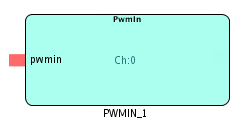

The PWM_INPUT block provides the ability to input a pulse pattern and measure the frequency and dutycycle of the input. This IP Core provides functionalities such as:

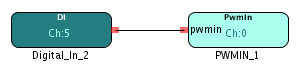

The digital input from the digital input block is connected to the PWM input block.