|

|

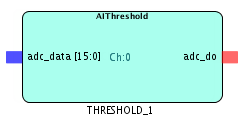

The ANALOG_THRESHOLD block provides the ability to ingest a multi-bit analog input signal and based on the the set thresholds create a single bit digital output. This IP Core provides functionality similar to Schmitt trigger devices which are typically used in signal conditioning applications to remove noise from analog signals. The ANALOG_THRESHOLD IP Core supports the following features:

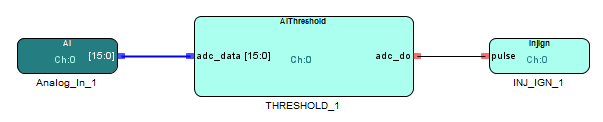

The analog intput from channel 0 is passed into the the threshold block. The thresholds are applied via the FPGAWB SDK API calls. Based on these thresholds the IP Core will create a digital output which is then passed into the INJ_IGN block to capture and time stamp the injection or ignition signals coming in.